🖥️ 페이징 가상 메모리 관리 🖥️

가상메모리는 간단하게

실행하고자 하는 프로그램을 일부만 메모리에 적재해서 실제 물리 메모리보다 큰 프로세스를 실행할 수 있게 하는 기술이다.

- 페이징, 세그멘테이션

만약 프로세스의 크기가 모두 동일하다면, 외부 단편화는 발생하지 않았을 것.

그럼 프로세스의 크기를 모두 동일하게 만들어 본다면?

페이징(paging)

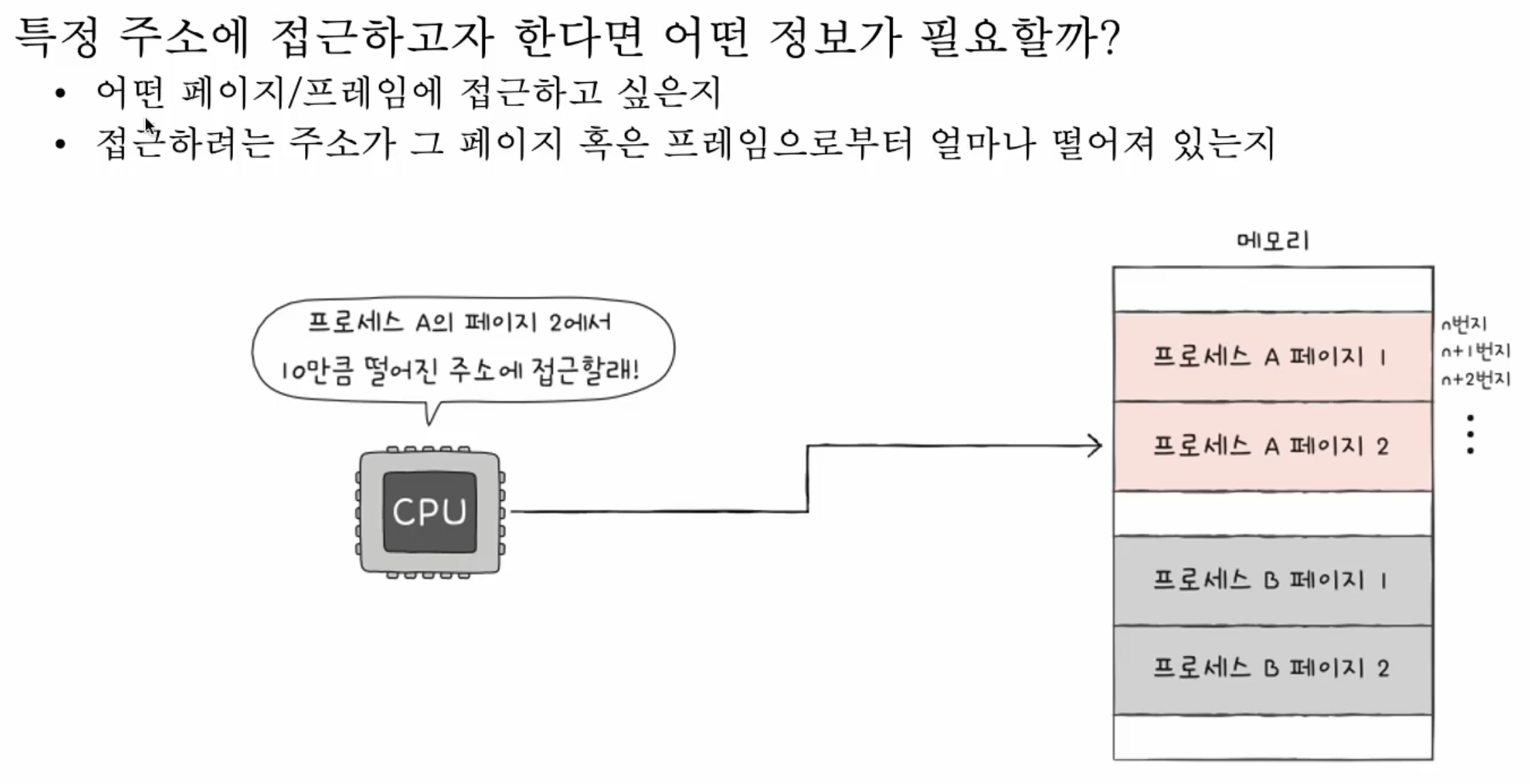

- 프로세스의 논리 주소 공간_(프로세스마다 0부터 N번지)을 페이지(page)라는 일정 단위로 자름.

- 메모리의 물리 주소 공간을 프레임(frame)이라는 페이지와 동일한 일정한 단위로 자름.

- 페이지를 프레임에 할당하는 가상 메모리 관리 기법

-> 스와핑이 가능하다? 특정 프로세스를 실행하기 위해 꼭 모든 페이지가 메모리에 있어야 하는 것은 아님을 시사함.

하지만

프로세스를 이루는 페이지가 어느 프레임에 적재되어 있는지 CPU가 일일이 알기가 어려움.

프로세스가 메모리에 불연속적으로 배치되어 있다면 CPU는 이를 순차적으로 실행할 수 없음.

즉 CPU 입장에서 다음에 실행할 명령어의 위치를 찾기가 어려워짐.

페이지 테이블

실제 메모리 내 주소인 물리 주소에(프레임에) 페이지들이 불연속적으로 배치되더라도,

CPU가 바라보는 주소인 논리 주소에는 연속적으로 배치되도록 하는 방법

즉 페이지 번호와 프레임 번호를 짝지어 주는 이정표 역할

하지만 페이징에서는 '내부 단편화' 문제가 발생한다.

쪼개면서 남는 공간이 생기는 것.

그래도 메모리 낭비의 크기가 외부 단편화에 비해 적을 확률이 높음.

CPU는 각각의 프로세스의 페이지 테이블을 어떻게 확인할 수 있을까?

PTBR은 프로세스의 페이지 테이블을 가리킴

근데 페이지 테이블이 메모리에 저장되어 있네..?

TLB에는 현재 자주 참조하고 있는 '페이지 테이블의 일부'가 저장되어 있음.

* Translation Lookaside Buffer_가상 메모리 주소를 물리적인 주소로 변환하는 속도를 높이기 위해 사용되는 캐시

(메모리 두 번 접근 대신, 캐시 메모리 한 번, 메모리 한 번)

페이지의 크기와 프레임의 크기도 동일하기 때문에 변위도 동일하다.

페이지 테이블 엔트리

유효 비트(valid bit)

현재 페이지가 스왑 영역에 있는지, 메모리에 있는지

보호 비트

ex. 코드 영역은 read-only다

참조 비트

수정 비트

쓰기 여부를 판단해 스왑 시 쓰기 작업을 거칠 수 있도록.

학습 출처: https://www.youtube.com/watch?v=bls_GjX-4U8&list=PLVsNizTWUw7FCS83JhC1vflK8OcLRG0Hl

'Computer Science > 운영체제' 카테고리의 다른 글

| 14. 페이지 교체와 프레임 할당 (0) | 2023.09.10 |

|---|---|

| 13. 쓰기 시 복사, 계층적 페이징 (0) | 2023.09.04 |

| 11. 연속 메모리 할당(적합, 외부 단편화, 압축) (0) | 2023.09.03 |

| 10. 교착 상태 해결 방법 (0) | 2023.09.02 |

| 9. 교착 상태(Dead Lock) (0) | 2023.09.02 |